# Invited: The Many PD Faces of Professor Jens Lienig

Andrew B. Kahng

abk@ucsd.edu

University of California, San Diego

La Jolla, CA, USA

## Abstract

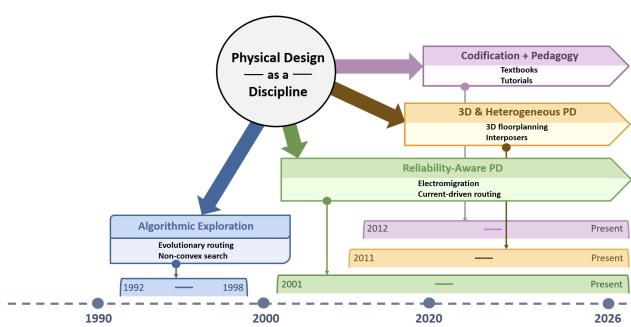

The 2026 ISPD Lifetime Achievement Award honors Professor Jens Lienig for his tremendous decades-long impact on physical design research, education, and community. Professor Lienig's career uniquely weaves algorithmic methodology, industry-driven foci, and pedagogical codification for future generations. It has both mirrored and driven the broadening of physical design's objective functions and notions of correctness, from geometric checks to reliability- and physics-aware methodologies. This invited paper provides a few personal perspectives to complement the excellent review by Knechtel et al. [47]. Three "PD faces" of Jens Lienig are highlighted: (i) early evolutionary and parallel metaheuristics for combinatorial problems in physical design; (ii) textbooks whose arc spans system context through layout practice and physical design automation, alongside landmark monographs on electromigration-aware design and 3D integration; and (iii) influence on the trajectory, research and community of ISPD.

## CCS Concepts

• Hardware → Electronic design automation; Wire routing; 3D integrated circuits; Hardware reliability; • Computing methodologies → Search methodologies.

## Keywords

VLSI Physical Design, Metaheuristics, Evolutionary Algorithms, Electromigration, Reliability, 3D Integration, Routing

### ACM Reference Format:

Andrew B. Kahng. 2026. Invited: The Many PD Faces of Professor Jens Lienig. In *Proceedings of the 2026 International Symposium on Physical Design (ISPD '26), March 15–18, 2026, Bonn, Germany*. ACM, New York, NY, USA, 6 pages. <https://doi.org/10.1145/3764386.3779615>

## 1 Introduction

It is both a privilege and a joy to take part in the recognition of Professor Jens Lienig as he receives the 15th ISPD Lifetime Achievement Award. When digging for foundational papers on a topic in physical design, one very frequently comes across Jens's work. Indeed, his name is one that students hear in the context of "As a first step, find and read everything that this person has written on (topic) – it begins there."

Throughout the collective 40-year history of the Physical Design Workshop (1987-1996) and the International Symposium on

Physical Design (1997-present), the scope of physical design (PD) has continually evolved. Objectives and constraints have expanded with the ever-growing breadth and complexity of manufacturing and integration technologies, device and circuit architectures, and the driving system products themselves. The PD community has repeatedly broadened its notion of "correctness", from geometric feasibility and wirelength, to timing, signal integrity, reliability and – increasingly – system-level and multiphysics considerations. A distinctive throughline in Jens's body of work is that it both *mirrors* and *drives* this broadening. His works have repeatedly proposed new PD problem statements, algorithms and methodologies that enhance our field's grounding in physics models, and elevate physical integrity and reliability as first-class design criteria.

This invited paper gives a personal perspective on Jens's contributions, complementing the excellent companion paper by Knechtel et al. [47]. Among the many "PD faces" of Jens Lienig, three are highlighted: (i) early evolutionary and parallel metaheuristics for combinatorial problems in physical design; (ii) textbooks whose arc spans system context through layout practice and physical design automation, alongside landmark monographs on electromigration-aware design and 3D integration; and (iii) influence on the trajectory, research and community of ISPD. Other dimensions and "PD faces" of Jens – his uniquely formative career trajectory, his works on analog IC design and hardware security, and more – are left to [47] and other accounts. The intent here is to highlight how Jens's pioneering ideas have been woven into the evolving agenda of the PD field and the ISPD community, and how his work helped to establish new PD objectives as mainstream concerns.

In the following, Section 2 provides biographical context: formative experiences in academia and industry, leading to technical contributions that shaped the PD field. Section 3 reviews Jens' early foundational works on metaheuristics: genetic algorithms and parallel search for routing and related PD problems, with novel concepts such as island models and diversity preservation. Section 4 discusses Jens' pedagogical impact and his codification of PD through a vertically-integrated series of "books for all design levels" [59]: textbooks that span system-level design, layout practice, and automation algorithms. Section 5 traces the community impact of two example research threads – electromigration-aware design and three-dimensional integration – within ISPD and the SLIP workshop. Section 6 concludes with reflections on the 2026 ISPD Lifetime Achievement Award and lasting themes of physically-grounded physical design that have been established by Jens's works.

## 2 Biographical Context

Jens received his doctorate in electrical and computer science, followed by early academic appointments where his research focused on evolutionary and population-based optimization methods for physical design, particularly routing. A postdoctoral fellowship at

This work is licensed under a Creative Commons Attribution 4.0 International License.

ISPD '26, Bonn, Germany

© 2026 Copyright held by the owner/author(s).

ACM ISBN 979-8-4007-2314-8/26/03

<https://doi.org/10.1145/3764386.3779615>

Concordia University (1991-1994) with Professor Krishnaiyan Thulasiraman led to such works as GASBOR [15] on switchbox routing. Then, during a visiting assistant professorship at the University of Virginia (1994-1996), Jens worked with Professors Jim Cohoon and Worthy Martin on the application of genetic algorithms (GA) to EDA problems, including routing. A recollection from Jens [55], referencing the seminal works [19] [21]: “I tried something new: Multiple populations (various sets of routing solutions calculated separately) that exchange from time to time genetic material (individual routing solutions). This became possible because the CS department at UVa had installed a network connecting a huge number of computers over the campus, which I exploited in a kind of “brute-force approach”. Quite tricky programming (mix of C language with scripts to handle the computer network’s flow), but it improved known results of standard routing benchmarks ...”

Jens subsequently gained extensive industrial experience at Tanner Research, Inc. (1996-1999), where he served as project manager and lead developer for the commercial place-and-route system L-Edit/SPR (Standard Cell Place and Route) – see Figure 1. (Jens and I first met at Tanner, when I gave a talk in the company’s conference room.) At Tanner, Jens’s contributions included (i) implementing 3-layer routing in such a way that further layers could be easily added later, and (ii) providing timing information (via SDF) both during and after place-and-route. His years at Tanner were both formative and memorable. Nearly 30 years afterward, a technical writer from the company, Ms. Judy Bergstresser, recalls Jens’s “attention to the precision and accuracy of the explication of his work, his intensive review, and reliable adherence to requested deadlines” [57].<sup>1</sup> And after further explicating Jens’s technical contributions (e.g., “Rather than simple wire-length minimization, he used fitness functions to weight and optimize signal integrity, timing slack, and power distribution”), Ms. Bergstresser concludes: “As a result, Tanner’s place and route module has migrated intact through acquisition first by Mentor and now at Siemens EDA, continuing to serve the mysterious art of analog/mixed-signal design for 30 years.” And Jens’s recollection adds: “I still remember those moments when JPL called in the afternoon because they encountered a routing bug and needed a fix the same day... The Martian rovers that roam(ed) on the red planet have those Tanner-tool-designed chips in them!”

Further industrial experience came at Robert Bosch GmbH (1999-2002), where Jens was CAD tool manager in the Design of Integrated Circuits division – now applying EDA tools, rather than designing or programming them. To address reliability challenges arising from current-density problems in sensor IC high-power traces, he initially worked to add current-density support (e.g., current-aware wire width selection) in the place-and-route flow. Jens then initiated the hiring of Göran Jerke, who became a long-standing collaborator on topics from wire planning to analog design automation. These experiences strongly influenced later research emphases on physically grounded, application-driven design methodologies.

Finally, since assuming the position of Full Professor and IFTE Director at TU Dresden (2002-present), Jens has established a world-leading research program that integrates algorithmic physical design, interconnect reliability, emerging integration technologies

<sup>1</sup>Jens’s 21st-century coauthors will be relieved to know that their experiences were not unique. It wasn’t them – it was Jens.

Fig. 1: Screenshot of the L-Edit/SPR place-and-route system [58].

and more. In parallel, he has played a significant role in physical design education and the training of a next generation through his series of textbooks covering electronic systems design, layout design, and physical design automation. As a result, his career has for 30 years been characterized by its close interactions among theory, industrial practice, teaching and mentoring.

**Three PD Faces.** The career trajectory recounted above maps naturally onto three of Jens’s “many PD faces”: (i) starting from computer science and algorithmics, the post-Ph.D. years in academia gave rise to Jens’s work on metaheuristics; (ii) the industry years at Tanner and Bosch subsequently motivated a broad agenda of reliability- and physics-driven research that found visibility at ISPD; and (iii) the TU Dresden years have woven these and other threads into a whole cloth of textbooks and sustained community engagement. These are each discussed in the following sections.

### 3 Evolutionary Optimization and Metaheuristics in PD

Jens’s early application of evolutionary optimization and metaheuristics to physical design [11–21] was prescient and far-reaching. Seeded primarily during his time at the University of Virginia, this body of work established lasting foundations and mindsets by not only acknowledging the scale of PD optimization, but embracing its inherently discrete, combinatorial, and rugged (i.e., in the sense of cost landscape) nature. Among the themes: (i) population-based (parallel) exploration is a principled response to structural hardness and scale; and (ii) complex objective functions and constraints must be met head-on.<sup>2</sup>

**Genetic algorithms for routing.** At a time when channel and switchbox routing tasks were largely approached using deterministic heuristics, Jens saw that the growing number of conflicting constraints – wirelength, via count, crosstalk, etc. – could not be robustly navigated by single-solution or purely greedy methods. His first works on evolutionary metaheuristics were in the context of Multi-Chip Module (MCM) designs and shrinking technology

<sup>2</sup>In other words: “first, assume a spherical horse” breaks down sooner than later, particularly in a PD universe of multiphysics, devices and interconnects, signoff and tapeout. That metaheuristics (annealing, GAs, etc.) flexibly handle “any cost function” was recognized early on, but only lately are such search-optimization paradigms coming back into fashion.

nodes [11, 13]. His response was to introduce genetic algorithms to routing and related PD problems [12, 16, 20], demonstrating that evolutionary search could yield competitive results on standard benchmarks.<sup>3</sup>

**Parallel search and island models.** Beyond adopting evolutionary computation in isolation, Jens developed parallel genetic algorithms that exploited distributed computing resources to maintain diversity and escape local optima. His work on island models, inspired by the biological concept of punctuated equilibria, formalized the idea that evolutionary metaheuristic outcomes are enhanced if multiple subpopulations evolve largely independently, with only infrequent migration of solutions [21]. The controlled exchange of genetic material preserves diversity and avoids stagnation, while enabling steady improvement; it was shown to outperform sequential evolutionary approaches on standard routing benchmarks in [14, 15].

**Looking back.** As described above, Jens's appointment at the University of Virginia brought serendipitous access to campus-wide distributed computing infrastructure that enabled large-scale parallel experimentation. The results demonstrated the power of evolutionary search for PD but revealed practical limitations (at that time): stochastic behavior, high computational cost, and sensitivity to parameter tuning. The work was consolidated in Jens's habilitation thesis (1996) but also led to a conclusion (at that time) of "not applicable to commercial design automation" [55].

Today, the context, conclusions and outlook for what Jens explored in the 1990s have all vastly changed: (i) the modern PD context demands accurate, detailed and scalable handling of complex PD objectives and constraints; (ii) cores, threads and VMs have become ever-more plentiful and accessible, while complementary infrastructure ranging from mature software stacks to LLM-based coding agents have lowered barriers tremendously; and (iii) a by-hook-or-by-crook focus on runtime- and compute-practical heuristics and metaheuristics has taken over (even in academic papers, there are now many fewer "theorems"). In parallel, phenomena such as "punctuated equilibria" are being rediscovered in large-scale ML model training; GA frameworks such as NSGA-II [45] are now widely used in EDA; and tools routinely leverage stochasticity and sampling (making lemonade from lemons) when confronted with discrete optimizations at huge scale.<sup>4</sup> Indeed, one can now foresee a PD future that will bring to fruition the original themes of Jens's early research – a future with "heavyweight" application of parallel metaheuristics (and solvers, including MILP, SAT, SMT) via population-based evolutionary and sampling paradigms.

## 4 Codification and Education

Jens is well-known for his dedication to pedagogy, which is perhaps most visible in the textbooks and monographs [1–10]. This contribution to our community goes beyond research algorithms, to the systematic codification and explanation of design. As explained in

<sup>3</sup>It is noteworthy that [13] ("An Evolutionary Algorithm for the Routing of Multi-Chip Modules") and [16] ("Genetic Algorithms Applied to the Physical Design of VLSI Circuits: A Survey") appeared respectively in the 3rd and 4th *Parallel Problem Solving from Nature* (PPSN) conferences, with the latter paper giving a survey of the paradigm 30 years ago. The PPSN/metaheuristics communities and research literatures are vast and rich – and arguably still too unfamiliar to PD and EDA, despite these early connections.

<sup>4</sup>After all, in many synthesis and optimization tasks, "only one thread needs to succeed".

the webpage "Books for all Design Levels" [59], Jens's textbooks seek to provide a unified pedagogical framework that spans electronic systems design; layout design of ICs, MCMs, and PCBs; and algorithms for physical design automation.<sup>5</sup> Viewed as a corpus, one can immediately see the consistent crispness, meticulous distillation and explanation of the essential concepts, clear illustrations, and other hallmarks of a great teacher.<sup>6</sup>

In the realm of physical design, Jens's books and monographs have translated industrial know-how and emerging topics into structured educational material, via works on layout synthesis [4, 7, 9], electromigration-aware design [6, 10], and three-dimensional electronic systems [2]. The defining characteristic of this body of work is its explicit orientation toward textbook use: rather than serving solely as reference material, the volumes are structured to support formal instruction, enabling adoption across a range of educational settings and shaping how PD concepts are introduced to students worldwide. This pedagogical "PD face" – the codification and perpetuation of knowledge – has helped to reinforce basic conceptual frameworks and maintain coherence of the field.

**Co-authorship of the VLSI Physical Design book.** Jens's 2006 German textbook *Layoutsynthese elektronischer Schaltungen* [4] presents the algorithmic core of layout synthesis: data structures and optimization techniques used in classical PD steps, from partitioning and floorplanning through routing and compaction.

Subsequently, over 14 years (October 2008 through June 2022) and two editions, I was privileged to co-author *VLSI Physical Design: From Graph Partitioning to Timing Closure* [1] [8] with Jens, Igor Markov and Jin Hu. Our project aimed to expand and modernize [4] for a broader audience. In brief, the first edition (2011) [1] added several modern PD and chip implementation aspects, including analytic placement, clock routing methods, detailed routing challenges, the multiobjective and coupled nature of design problems, and an extended treatment of timing closure. The second edition (2022) [8] brought additional polish, improved figures (in color when crucial for understanding), and various updates to reflect the increasing complexity of chip implementation in nanometer-scale nodes. Notably, the second edition acknowledges the paradigm shift toward data-driven methodologies with the addition of an appendix dedicated to machine learning applications in physical design.

Hundreds of emails (many with detailed reminders and updates); a large box of chapter hardcopies<sup>7</sup>; and the usage and adoption of *VLSI Physical Design* itself (including translation into Mandarin) – are reminders of how Jens's personal drive and determination underlie this book and doubtless his other books as well. Jens spent years on writing, and on making thousands of catches and fixes through the editing and production processes. Equally crucial were his efforts to compile and openly disseminate figures and lecture slides [61] for instructors and students to freely use; to place copies of the book in major university libraries so that it could be freely browsed; and to translate it (even if unofficially) into other languages so that non-English readers could access it. (Why does one

<sup>5</sup>Or, as Jens puts it, "[f]rom explaining systems to explaining designing components and then to design automation ... written such that they can be used as textbooks" [55].

<sup>6</sup>For example, the presentation of Electronics Technologies (spanning printed circuit board, hybrid, and semiconductor) in just 11 pages at the outset of [9] is remarkable (as is the overall book itself).

<sup>7</sup>Unfortunately, a somewhat 'triggering' reminder of Springer's MS Word template ...

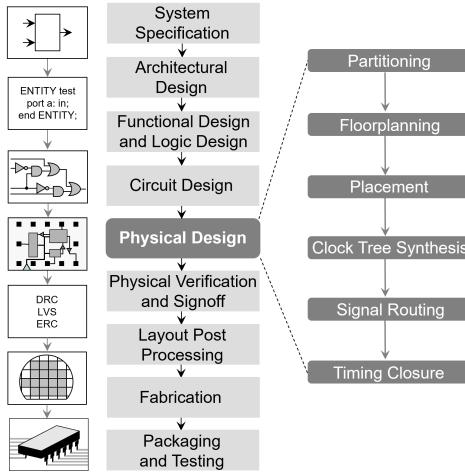

so often come across the physical design flowchart in Figure 2? Because Jens made sure that this figure from the book was made public under a Creative Commons license!) In this way, Jens provided the spark and motive force for the arc from algorithmic focus in *Layoutsynthese* to timing closure- and ML-awareness in *VLSI Physical Design*, and for the arc of the latter's adoption in PD education.

Fig. 2: Physical design flow figure from Wikipedia article “Physical design (electronics)” [60], adapted from [1].

**Bridging automation and implementation.** While [8] emphasizes the automation of physical design, Jens's *Fundamentals of Layout Design for Electronic Circuits* with Jürgen Scheible [7, 9] focuses on the practical implementation of layout. It is a (personal) favorite for how it cohesively defines and occupies a distinct position between circuit design texts such as [51, 52] and algorithm-centric PD texts such as [53, 54]. [7, 9] succinctly integrates lithographic patterning, fabrication constraints, analog matching, power grids, and packaging interactions – bringing in the physical realities and constraints that govern layout geometries. In doing so, the book fills a gap in many university curricula by explicitly capturing the “art of layout design” – the hands-on experience-driven aspects of layout design that are often underrepresented in automation-focused treatments.

**Specialized monographs: reliability and 3D integration.** Beyond pure textbooks, Jens has found time to write specialized monographs that distill key research trajectories and translate awareness of complex physical phenomena into concrete design methodologies. His book on electromigration-aware design [6] [10], now in its second edition, connects materials and reliability physics to concrete layout methodologies such as current-driven routing and reliability-aware decompaction. And, his 2012 book on three-dimensional electronic systems [2] is a timely reflection of the looming importance of heterogeneous integration: it provides a concise and still-relevant curriculum that covers through-silicon vias, thermal management, and stacked-die integration.

## 5 Impacts on ISPD Itself

The preceding sections have described two faces of Jens's PD contributions: (i) foundations of evolutionary metaheuristic and parallel optimization (Section 3), and (ii) pedagogical codification through textbooks that span system design through physical design automation (Section 4). A third face comprises Jens's impacts *on ISPD itself*: how he has brought new research directions into the technical foreground of ISPD and its community. Two research threads in particular – electromigration-aware design and three-dimensional integration – have found sustained visibility within the ISPD community. Their shared trajectory is one of industrial problem recognition, physically-grounded optimization methods, and adoption by the community as a recognized dimension of physical design.<sup>8</sup>

**Electromigration-aware physical design at ISPD.** In the early 2000s, Jens's research started to focus on electromigration (EM) and current density as central PD concerns. This was driven by industrial product design needs, and led to works such as [22–34]. As noted above (Section 2), work at Robert Bosch GmbH catalyzed this transition: high-power sensor interconnects exposed the limitations of treating reliability as a post-layout check, and this motivated development of methods that could embed current-density constraints directly into physical design optimizations [22, 23, 26, 27].

EM reliability-driven layout became part of ISPD with Jens's seminal ISPD 2006 paper [34] and the very memorable accompanying presentation.<sup>9</sup> This work provided one of the earliest systematic introductions to electromigration-aware physical design for ISPD audience members, explicitly framing EM as a PD problem rather than as a post-design verification issue. Contemporaneous tutorials and embedded presentations such as [28, 33] reinforced the message that physical correctness would depend on explicitly modeling electrical stress during layout synthesis.

Subsequent ISPD contributions extended this message from awareness of a physical reliability mechanism to concrete algorithmic mitigations and community-level advocacy. Work on load-aware redundant via insertion demonstrated practical EM-aware optimization within PD flows [30] [31], while other works emphasized the growing severity of electromigration in advanced technologies and the need for proactive, design-time methodologies [29]. An influential ISPD 2018 paper framed the pressing need for systematic electromigration-aware physical design as a field-wide challenge [32]. Collectively, these contributions define a clear trajectory – from industrial problem recognition, to algorithmic solutions, to community adoption – by which electromigration evolved from a specialized reliability issue into a recognized and enduring dimension of physical design research.

The trajectory is furthermore mirrored by pedagogical efforts. Notably, Jens's monograph on electromigration-aware design [6] [10] codifies the field's accumulated understanding, enabling new researchers to engage with EM-aware PD as an established domain of research and practice, rather than as a scattered set of papers and techniques.

<sup>8</sup>While the discussion here is brief, Jens's contributions in these areas are well-summarized in [47].

<sup>9</sup>The talk and its slides left a deep impression. It was also at that moment that I first realized Jens's gifts as a teacher.

**Physical design for 3D and heterogeneous integration.** Jens's works on physical design for three-dimensional (3D) integration [35–44] have also contributed to the evolution of ISPD. Here again, Jens's works apply physically-grounded design perspectives to emerging 3D PD challenges. Early works investigated layout representations and interconnect prediction for 3D technologies [37, 41]; this was followed by studies of 2D block assembly into 3D chips [43] and massive-scale interconnects [42]. Together, these efforts opened up fundamental issues of connectivity, deadspace, and structural planning in vertically integrated systems.

Subsequent research emphasized multi-objective optimization in 3D PD, incorporating deadspace, voltage assignment, and interconnect considerations [36, 38]. Work on interposer-based systems further highlighted the need for physically faithful models when determining die placement and interconnect structure [40]. And, at ISPD 2016, Knechtel and Lienig outlined challenges and solutions for 3D PD automation [39].

Through this body of work, consistent themes reappear: (i) integration density amplifies physical effects, reinforcing the need for reliability- and physics-aware design methodologies; and (ii) rather than abstracting away complexity, 3D physical design must incorporate richer models that accurately capture the physics realities and challenges of advanced integration. As with electromigration, pedagogy strongly complements research: the volume on three-dimensional electronic systems [2] codifies the state of the field for students, researchers and practitioners alike.

## 6 The ISPD 2026 Lifetime Achievement Award

Over his 35-year career, Professor Jens Lienig has made pioneering contributions to multiple domains of physical design research, while remaining consistently grounded in physical realism and practical relevance. His “many PD faces” span algorithmic and metaheuristic foundations, reliability-driven methodology, three-dimensional integration, education and codification of knowledge, and much more.

Fig. 3: Facets and faces of PD seen in works of Jens Lienig.

Figure 3 shows the several “PD faces” that have been discussed. Jens's early research on metaheuristic optimization helped establish population-based exploration as a principled response to the scale and discrete, multi-objective nature of physical design problems. Later, his work on electromigration and interconnect reliability advanced the integration of physical stress considerations directly

into design-time algorithms, changing how physical reliability is addressed by physical design flows. He extended this physically-grounded perspective to emerging 3D integration contexts, where interconnect modeling, layout structure, and physical effects are tightly coupled.

Through his sustained engagement with ISPD and its community, as well as his authorship of widely used textbooks, Jens has helped shape a shared conceptual framework that connects optimization algorithms, physical phenomena, and real-world design constraints. His work has strengthened the continuum of research, teaching and practice while establishing physically-grounded physical design as a central mindset for how our field defines and addresses its core problems. The 2026 ISPD Lifetime Achievement Award celebrates these achievements and impacts with admiration, respect and gratitude. Congratulations, Jens!

## Acknowledgments

Many thanks to Yiting Liu and Bodhisatta Pramanik for their tremendous help with the figures and text in this paper. Correspondences with Susann Rothe, Johann Knechtel, and Jens Lienig himself provided unique background elements that are reflected here. Thanks are also due to the ISPD 2026 organizers for their warm invitation to write down this perspective, and to authors of [47] for graciously sharing early views of their paper.

## References

- [1] A. B. Kahng, J. Lienig, I. L. Markov, and J. Hu, *VLSI Physical Design: From Graph Partitioning to Timing Closure*, 1st ed., Springer, 2011.

- [2] J. Lienig and M. Dietrich, *Entwurf integrierter 3D-Systeme der Elektronik*, Springer, 2012.

- [3] J. Lienig and H. Bruemmer, *Elektronische Gerätetechnik*, Springer, 2014.

- [4] J. Lienig, *Layoutsynthese elektronischer Schaltungen*, Springer, 2016. (Originally published as: *Layoutsynthese elektronischer Schaltungen – Grundlegende Algorithmen für die Entwurfsautomatisierung*, Springer Verlag 2006, ISBN 3-540-29627-1.)

- [5] J. Lienig and H. Bruemmer, *Fundamentals of Electronic Systems Design*, Springer, 2017.

- [6] J. Lienig and M. Thiele, *Fundamentals of Electromigration-aware Integrated Circuit Design*, 1st ed., Springer, 2018.

- [7] J. Lienig and J. Scheible, *Fundamentals of Layout Design for Electronic Circuits*, Springer, 2020.

- [8] A. B. Kahng, J. Lienig, I. L. Markov, and J. Hu, *VLSI Physical Design: From Graph Partitioning to Timing Closure*, 2nd ed., Springer, 2022.

- [9] J. Lienig and J. Scheible, *Grundlagen des Layoutentwurfs elektronischer Schaltungen*, Springer, 2023.

- [10] J. Lienig, S. Rothe, and M. Thiele, *Fundamentals of Electromigration-aware Integrated Circuit Design*, 2nd ed., Springer, 2025.

- [11] J. Lienig, K. Thulasiraman, and M. N. S. Swamy, “Routing Algorithms for Multi-Chip Modules”, *Proc. EURO-DAC*, 1992, pp. 286-291.

- [12] J. Lienig and K. Thulasiraman, “A Genetic Algorithm for Channel Routing in VLSI Circuits”, *Evolutionary Computation* 1(4) (1994), pp. 293-311.

- [13] J. Lienig and H. Brandt, “An Evolutionary Algorithm for the Routing of Multi-Chip Modules”, *International Conference on Parallel Problem Solving from Nature*, 1994, pp. 588-597.

- [14] J. Lienig, “A Parallel Genetic Algorithm For Two Detailed Routing Problems”, *Proc. ISCAS*, 1996, pp. 508-511.

- [15] J. Lienig and K. Thulasiraman, “GASBOR: A Genetic Algorithm Approach for Solving the Switchbox Routing Problem”, *Journal of Circuits, Systems and Computers* 6(4) (1996), pp. 359-373.

- [16] J. Lienig and J. P. Cohoon, “Genetic Algorithms Applied to the Physical Design of VLSI Circuits: A Survey”, *International Conference on Parallel Problem Solving from Nature*, 1996, pp. 839-848.

- [17] J. Cohoon, J. Karro, and J. Lienig, “Evolutionary Algorithms for the Physical Design of VLSI Circuits”, *Advances in Evolutionary Computing: Theory and Applications*, Springer, 2003, pp. 683-711.

- [18] J. Lienig, “Channel and Switchbox Routing with Minimized Crosstalk - A Parallel Genetic Algorithm Approach”, *Proc. VLSID*, 1997, pp. 27-31.

- [19] J. Lienig, “A Parallel Genetic Algorithm for Performance-Driven VLSI Routing”, *IEEE Trans. Evolutionary Computation* 1(1) (1997), pp. 29-39.

[20] J. Lienig, "Physical Design of VLSI Circuits and the Application of Genetic Algorithms", *Evolutionary Algorithms in Engineering Applications*, Springer, 1997, pp. 277-292.

[21] W. N. Martin, J. Lienig, and J. P. Cohoon, "Island (Migration) Models: Evolutionary Algorithms based on Punctuated Equilibria", *Handbook of Evolutionary Computation*, IOP and Oxford University Press, 1997, pp. C6.3.1-C6.3.16.

[22] J. Lienig, G. Jerke, and T. Adler, "AnalogRouter: A New Approach of Current-Driven Routing for Analog Circuits", *Proc. DATE*, 2001, pp. 0819-0819.

[23] G. Jerke and J. Lienig, "Hierarchical Current Density Verification for Electromigration Analysis in Arbitrarily Shaped Metallization Patterns of Analog Circuits", *Proc. DATE*, 2002, pp. 464-469.

[24] J. Lienig, G. Jerke, and T. Adler, "Electromigration Avoidance in Analog Circuits: Two Methodologies for Current-Driven Routing", *Proc. ASP-DAC*, 2002, pp. 372-378.

[25] J. Lienig and G. Jerke, "Current-driven Wire Planning for Electromigration Avoidance in Analog Circuits", *Proc. ASP-DAC*, 2003, pp. 783-788.

[26] G. Jerke and J. Lienig, "Hierarchical Current-Density Verification in Arbitrarily Shaped Metallization Patterns of Analog Circuits", *IEEE Trans. on CAD* 23(1) (2004), pp. 80-90.

[27] C. Jerke, J. Lienig, and J. Scheible, "Reliability-driven Layout Decompaction for Electromigration Failure Avoidance in Complex Mixed-signal IC Designs", *Proc. DAC*, 2004, pp. 181-184.

[28] J. Lienig and G. Jerke, "Embedded Tutorial: Electromigration-Aware Physical Design of Integrated Circuits", *Proc. VLSID*, 2005, pp. 77-82.

[29] J. Lienig, "Electromigration and Its Impact on Physical Design in Future Technologies", *Proc. ISPD*, 2013, pp. 33-40.

[30] S. Bigalke and J. Lienig, "Load-aware Redundant Via Insertion for Electromigration Avoidance", *Proc. ISPD*, 2016, pp. 99-106.

[31] S. Bigalke, J. Lienig, G. Jerke, J. Scheible, and R. Jancke, "The Need and Opportunities of Electromigration-aware Integrated Circuit Design", *Proc. ICCAD*, 2018, pp. 1-8.

[32] J. Lienig and M. Thiele, "The Pressing Need for Electromigration-aware Physical Design", *Proc. ISPD*, 2018, pp. 144-151.

[33] J. Lienig, "Interconnect and Current Density Stress: an Introduction to Electromigration-aware Design", *Proc. SLIP*, 2005, pp. 81-88.

[34] J. Lienig, "Introduction to Electromigration-aware Physical Design", *Proc. ISPD*, 2006, pp. 39-46.

[35] J. Knechtel, E. F. Y. Young, and J. Lienig, "Structural Planning of 3D-IC Interconnects by Block Alignment", *Proc. ASP-DAC*, 2014, pp. 53-60.

[36] J. Knechtel, J. Lienig, and I. M. Elfadel, "Multi-objective 3D Floorplanning with Integrated Voltage Assignment", *ACM Trans. on DAES* 23(2) (2018), pp. 1-27.

[37] R. Fischbach, J. Lienig, and J. Knechtel, "Investigating Modern Layout Representations for Improved 3D Design Automation", *Proc. GLSVLSI*, 2011, pp. 337-342.

[38] J. Knechtel, I. L. Markov, J. Lienig, and M. Thiele, "Multiobjective Optimization of Deadspace, a Critical Resource for 3D-IC Integration", *Proc. ICCAD*, 2012, pp. 705-712.

[39] J. Knechtel and J. Lienig, "Physical Design Automation for 3D Chip Stacks: Challenges and Solutions", *Proc. ISPD*, 2016, pp. 3-10.

[40] S. Osmolovskyi, J. Knechtel, I. L. Markov, and J. Lienig, "Optimal Die Placement for Interposer-based 3D ICs", *Proc. ASP-DAC*, 2018, pp. 513-520.

[41] R. Fischbach, J. Lienig, and T. Meister, "From 3D Circuit Technologies and Data Structures to Interconnect Prediction", *Proc. SLIP*, 2009, pp. 77-84.

[42] J. Knechtel, E. F. Y. Young, and J. Lienig, "Planning Massive Interconnects in 3-D Chips", *IEEE Trans. on CAD* 34(11) (2015), pp. 1808-1821.

[43] J. Knechtel, I. L. Markov, and J. Lienig, "Assembling 2D Blocks into 3D Chips", *Proc. ISPD*, 2011, pp. 81-88.

[44] J. Knechtel, O. Sinanoglu, I. M. Elfadel, J. Lienig, and C. C. N. Sze, "Large-scale 3D chips: Challenges and Solutions for Design Automation, Testing, and Trustworthy Integration", *IPSJ Trans. on System and LSI Design Methodology* 10 (2017), pp. 45-62.

[45] K. Deb, A. Pratap, S. Agarwal, and T. Meyarivan, "A Fast and Elitist Multiobjective Genetic Algorithm: NSGA-II", *IEEE Trans. on Evolutionary Computation* 6(2) (2002), pp. 182-197.

[46] G. Gourdoumanis, F. Oikonomou, M. Pantazi-Kypraiou, P. Stoikos, O. Axelou, A. Tziouvaras, G. Karakonstantis, T. Aladwani, C. Anagnostopoulos, Y. Shen, A. Pathania, A. Garcia-Ortiz, and G. Floros "Multi-Partner Project: COIN-3D – Collaborative Innovation in 3D VLSI Reliability", to appear in *Proc. DATE*, 2026. Also: <https://arxiv.org/abs/2601.14347>.

[47] J. Knechtel, S. Rothe, R. Fischbach, M. Thiele, T. Meister, and A. Krinke, "Invited: From Evolutionary Algorithms to Analog Design, Electromigration, 3D Integration, and Beyond: On Jens Lienig's Contributions to Advance Physical Design", *Proc. ISPD*, 2026.

[48] M. Jaderberg, V. Dalibard, S. Osindero, W. M. Czarnecki, J. Donahue, A. Razavi, O. Vinyals, T. Green, I. Dunning, K. Simonyan, and D. Hassabis, "Population Based Training of Neural Networks", *arXiv preprint arXiv:1711.09846*, 2017.

[49] H. B. McMahan, E. Moore, D. Ramage, S. Hampson, and B. Agüera y Arcas, "Communication-Efficient Learning of Deep Networks from Decentralized Data", *Proc. AISTATS*, 2017, pp. 1273-1282.

[50] Justin K. Pugh, L. B. Soros, and Kenneth O. Stanley, "Quality Diversity: A New Frontier for Evolutionary Computation", *Frontiers in Robotics and AI* 3(40) (2016), pp. 1-17.

[51] J. M. Rabaey, A. P. Chandrakasan, and B. Nikolic, *Digital Integrated Circuits: A Design Perspective*, 2nd ed., Upper Saddle River, Pearson, 2003.

[52] N. H. E. Weste and D. M. Harris, *CMOS VLSI Design: A Circuits and Systems Perspective*, Boston, Addison-Wesley, 2011.

[53] N. A. Sherwani, *Algorithms for VLSI Physical Design Automation*, 3rd ed., Boston, Kluwer Academic Publishers, 1999.

[54] M. Sarrafzadeh and C. K. Wong, *An Introduction to VLSI Physical Design*, New York, McGraw-Hill, 1996.

[55] J. Lienig, *personal communication*, Dec. 2025.

[56] S. Rothe, *personal communication*, Jan. 2026.

[57] J. Bergstresser, *personal communication*, Jan. 2026.

[58] L-Edit screenshot. <https://www.eda-solutions.com/products/l-edit-ic-layout/>

[59] Books for all Design Levels. <https://www.layoutentwurf.de/>

[60] "Physical design (electronics)", *Wikipedia article*. [https://en.wikipedia.org/wiki/Physical\\_design\\_%28electronics%29](https://en.wikipedia.org/wiki/Physical_design_%28electronics%29).

[61] VLSI Physical Design book website at IFTE. <https://www.ifte.de/books/eda/index.html>