## **Clock Area**

- Clock networks consume silicon area (clock drivers, PLL, etc.) and routing area

- Routing area is most vital

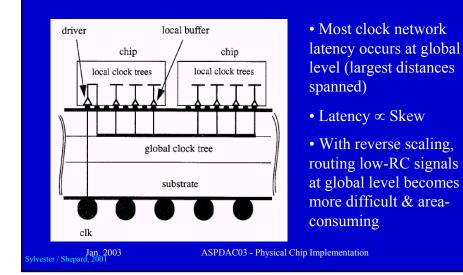

- Top-level metals are used to reduce RC delays

- These levels are precious resources (unscaled)

- Power routing, clock routing, key global signals

- Reducing area also reduces wiring capacitance and power

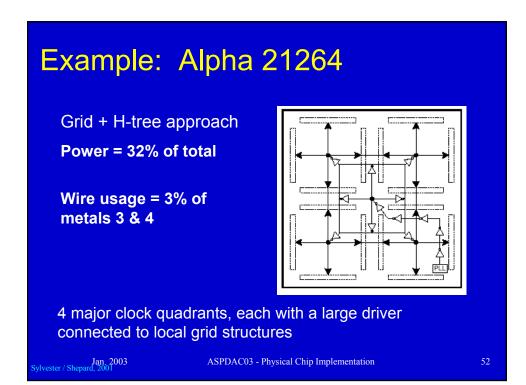

- Typical #'s: Intel Itanium 4% of M4/5 used in clock routing

ASPDAC03 - Physical Chip Implementation

# **Clock Distribution Trends**

### Timing

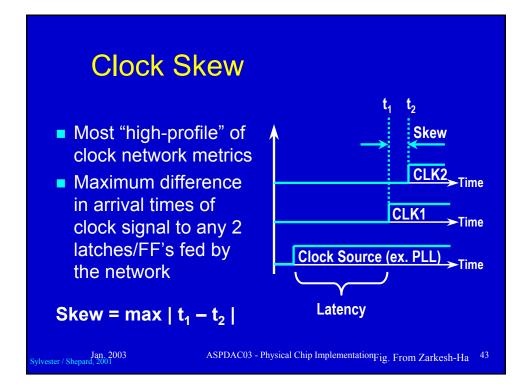

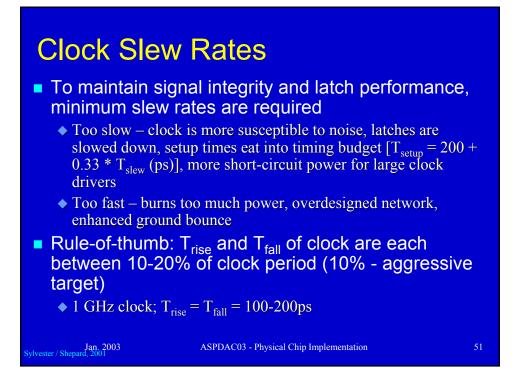

- Clock period dropping fast, skew must follow

- ◆ Slew rates must also scale with cycle time

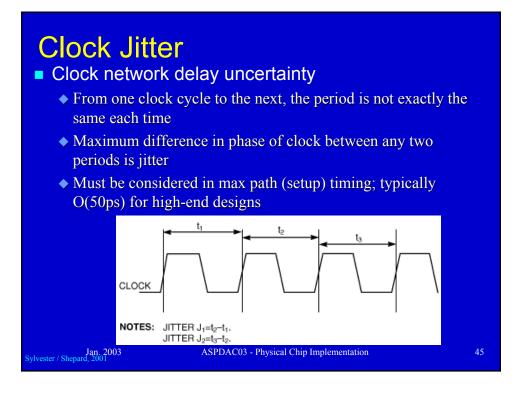

- Jitter PLL's get better with CMOS scaling but other sources of noise increase

- Power supply noise more important

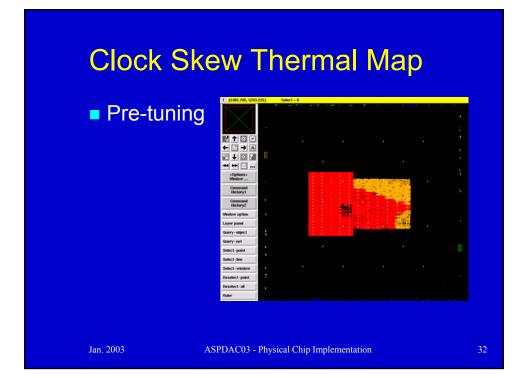

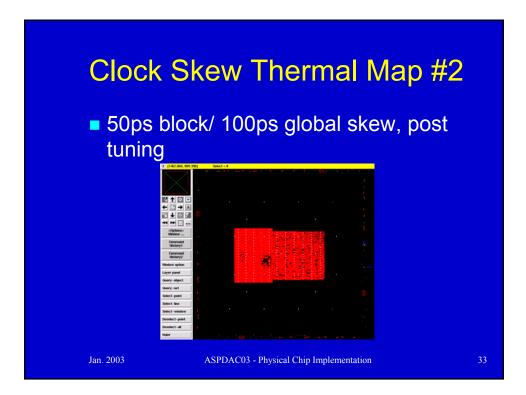

- Switching-dependent temperature gradients

### Materials

- ◆ Cu reduces RC slew degradation, potential skew

- ◆ Low-k decreases power, improves latency, skew, slews

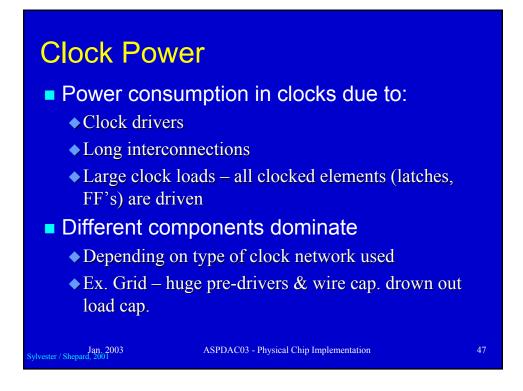

- Power

- ♦ Complexity, dynamic logic, pipelining → more clock sinks

- Larger chips  $\rightarrow$  bigger clock networks

Jan. 2003 Sylvester / Shepard, 2001 ASPDAC03 - Physical Chip Implementation

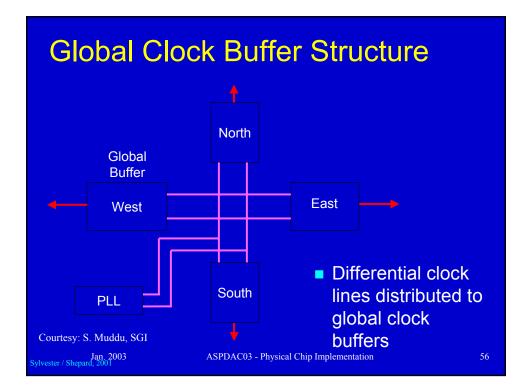

## **Hierarchy Management**

#### Mini-Block level Clock

- Count clock nodes per Std. Block

- total load (gate + wire)

- Determine local clock tree levels/size

- Estimate size of area clock buffer

- Reserve space for clock buffers and clock wires/shields

- Apply balanced clock routing

#### Top-level Clock

- Add clock grid topology for each Std. block

- Estimate PLL to local buf. delays for all Std.blocks

- Determine worst case delay

- ◆ Add buffer-chains to align delays

- Consider electromigration for high-activity, heavily-loaded wires

- Add shielding inside, if necessary

- Top-level balanced clock routing

#### Courtesy: S. Muddu, SGI

Jan. 2003 Sylvester / Shepard, 2001 ASPDAC03 - Physical Chip Implementation

#### **Grid Networks** Predrivers Gridded clock distribution common on earlier DEC Alpha microprocessors Advantages: Skew determined by grid density, not too sensitive to load position Global Clock signals available everywhere grid Tolerant to process variations Usually yields extremely low skew values Disadvantages: ◆ Huge amount of wiring and power ◆ To minimize such penalties, need to make grid pitch coarser $\rightarrow$ lose the grid advantage Jan. 2003 Sylvester / Shepard, 2001 ASPDAC03 - Physical Chip Implementation 58

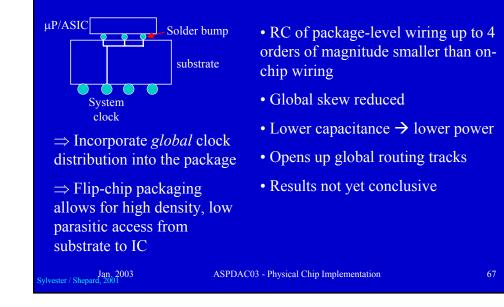

# **Skew Reduction Using Package**

## **Skew Reduction Using Package**