# Co-Optimization of Memory BIST Grouping, Test Scheduling, and Logic Placement

Andrew B. Kahng<sup>†‡</sup> and Ilgweon Kang<sup>‡</sup>

UC San Diego ECE<sup>†</sup> and CSE<sup>‡</sup> Departments, La Jolla, CA 92093

{abk, igkang}@ucsd.edu

Abstract-Built-in self-test (BIST) is a well-known design technique in which part of a circuit is used to test the circuit itself. BIST plays an important role for embedded memories, which do not have pins or pads exposed toward the periphery of the chip for testing with automatic test equipment. With the rapidly increasing number of embedded memories in modern SOCs (up to hundreds of memories in each hard macro of the SOC), product designers incur substantial costs of test time (subject to possible power constraints) and BIST logic physical resources (area, routing, power). However, only limited previous work addresses the physical design optimization of BIST logic; notably, Chien et al. [7] optimize BIST design with respect to test time, routing length, and area. In our work, we propose a new three-step heuristic approach to minimize test time as well as test physical layout resources, subject to given upper bounds on power consumption. A key contribution is an integer linear programming ILP framework that determines optimal test time for a given cluster of memories using either one or two BIST controllers, subject to test power limits and with full comprehension of available serialization and parallelization. Our heuristic approach integrates (i) generation of a hypergraph over the memories, with test time-aware weighting of hyperedges, along with top-down, FM-style min-cut partitioning; (ii) solution of an ILP that comprehends parallel and serial testing to optimize test scheduling per BIST controller; and (iii) placement of BIST logic to minimize routing and buffering costs. When evaluated on hard macros from a recent industrial 28nm networking SOC, our heuristic solutions reduce test time estimates by up to 11.57% with strictly fewer BIST controllers per hard macro, compared to the industrial solutions.

## I. INTRODUCTION

In modern SOCs, embedded memories (normally, SRAM blocks) can account for more than 50% of die area [25]. Since a defect in embedded memory can make the entire chip fail, design for test (DFT) techniques for embedded memory are essential. *Built-in self-test* (BIST) is an increasingly effective and necessary DFT technique in which part of a circuit is used to test the circuit itself [1]. In particular, BIST is now ubiquitous for embedded memories, which do not have pins or pads exposed for testing with automated test equipment (ATE).

Memory BIST affects design quality and chip cost in several basic ways.

- BIST controller logic occupies silicon real estate, and contributes to die area, leakage power, and routing congestion. All else being equal, the fewer BIST controller blocks, the better.

- The widths and depths of embedded memories assigned to a given BIST controller must be "packed" into a feasible test schedule that minimizes test time subject to maximum power constraints. The test time directly impacts product cost and is a first-class design consideration, especially in a design with many memories.

- The physical placement of a BIST controller logic block relative to its associated memory blocks affects not only routability, but also the signal delay between the controller and the memories. Larger distances force the use of more buffering and lower- $V_T$  devices to meet timing and electrical constraints; this costs more power.

From these considerations, it is apparent that the co-optimization of physical design resources, test power, leakage power, and test time falls between front-end DFT groups and back-end physical design groups. On the one hand, a floorplan-oblivious partitioning of memories to BIST controllers might force use of low- $V_T$  (LVT) cells to meet timing requirements. On the other hand, the physical design (PD) engineer's suggested partitioning may lead to less congestion, routing cost, and signal delay between memories and BIST logic, but with dramatically increased test time.

In this paper, we describe a heuristic optimization that smooths the interactions between front-end DFT and back-end PD, reducing iterations and schedule costs. Our heuristic minimizes test time as well as test physical layout resources, subject to given upper bounds on power consumption. A new integer linear program (ILP) formulation finds the optimal test time for a given cluster of memories using either one or two BIST controllers, taking full advantage of any available serialization and parallelization of the memory self-test. When evaluated on hard macros from a recent industrial 28nm networking SOC, our heuristic solutions reduce test time estimates by up to 11.57% with strictly fewer BIST controllers per hard macro, compared to the industrial solutions.

Our main contributions can be summarized as follows.

- We propose a weighted hypergraph construction that allows use of top-down min-cut partitioning of memories into clusters that have good physical design and test scheduling attributes.

- We propose an ILP that comprehends parallel and serial testing of a given group of memories as it finds a minimum-test time solution with one or two BIST controllers.

- We use the above two elements, along with bottleneck matching to find BIST logic placement locations, in a heuristic that simultaneously reduces both BIST logic and test time costs in hard macros from a recent 28nm networking SOC.

In the remainder of this paper, Section II briefly reviews related works in the areas of test scheduling and memory BIST. Section III describes our ILP formulation to minimize test time taking advantage of available serialization and parallelization. Section IV presents our heuristic approach, and Section V gives experimental results with industrial testcases. Section VI describes directions of ongoing work and concludes the paper.

# II. RELATED WORKS

In this section, we broadly classify related literature as dealing with (1) test scheduling and (2) BIST controller optimizations.

# A. Test Scheduling

Test time reduction has long been a basic goal of DFT research, since test time is directly related to test cost. Parallel (simultaneous) testing reduces test time but is constrained by power and bandwidth (pin count) limits. Works such as that of Yao et al. [20], formulate and solve the test scheduling problem to minimize total test time while satisfying such constraints. Iyengar et al. [12] [13] adapt a rectangle packing problem formulation to test scheduling; they co-optimize test access mechanism (TAM) architecture and test wrapper, while designating a group of tests. Zou et al. [21] formulate SOC test scheduling as two-dimensional bin packing under given pin constraints, and simulated annealing is used to search for a heuristic optimum test schedule by perturbations to an initial solution.

Other researchers have applied integer linear programming (ILP) to find optimal test schedules under constraints [5] [6] [8] [15]. Chakrabarty [5] proposes test access architectures that incorporate place-and-route constraints arising from interconnections. [6] uses mixed integer-linear programming (MILP) to optimize test schedules for core-based systems; a heuristic algorithm efficiently solves larger problem instances for which the MILP approach has excessive runtime. Liu et al. [15] apply ILP formulation for NOC instances. Chin and Nourani [8] propose a flexible ILP-based test scheduling environment with many user options.

Wang et al. [19] develop a test scheduling algorithm based on elements of the March algorithm for memory BIST; the objective is to minimize overall testing time under a power constraint.

Unlike previous works, we study the minimization of total test time in the context of a *mixture of serial and parallel testing, with multiple memory BIST controllers, by considering physical information*  *of memories.*<sup>1</sup> We note that most of the previous literature on test scheduling addresses scheduling for logic cores, where the testing is mainly performed by scan chain techniques. By contrast, we address embedded memory testing using multiple memory BIST controllers, where the memories have different sizes, test times, and test power values.

#### B. Design Optimizations for Memory BIST Controllers

Most works in the memory BIST literature focus on architectural and testing aspects, even though design optimization of memory BIST can provide substantial benefits to the entire chip design and to test quality. To our knowledge, relatively few works exist in the realm of (physically-aware) design optimization of memory BIST.<sup>2</sup>

A memory grouping method for sharing memory BIST logic is proposed by Miyazaki et al. in [17]. Area overhead reductions are achieved by the grouping of memories for parallel and serial testing. Devanathan et al. [9] propose a physically-aware memory BIST datapath synthesis framework, wherein a hierarchical synthesis approach achieves correct-by-construction, area-efficient memory BIST solutions. Devanathan et al. demonstrate the benefits from strategic approaches to physically-aware BIST in [11] and built-in selfrepair (BISR) design optimization methods in [10]: such techniques mitigate the difficulties of physical design closure such as congestion and timing closure, even as the numbers of memory instances and BIST controllers in complex SOCs continue to increase. The authors of [10] [11] also note that their methods enable designers to apply more effective tests and reduce verification cycle times.

Chien et al. [7] propose a memory BIST design optimization method to minimize test time, wire length and total area while considering several practical design constraints. To our knowledge, [7] is the first published work considering aspects of physical design for memory BIST controllers. The authors adopt an integer linear programming (ILP) formulation for the assignment of memories to controllers. They then apply legalization and refinement steps to meet user-specified constraints and to further improve the quality of their solution. Although [7] is the previous work that is closest to ours, we observe that it makes a number of simplifications that we avoid, e.g., (i) all memory instances in a BIST cluster are tested in parallel (leading to an unrealistic test time estimate); and (ii) only one cluster is tested at a time (preventing exploitation of parallel testing with multiple BIST controllers).<sup>3</sup>

#### **III. ILP FORMULATION**

We develop an integer linear program (ILP) to solve the memory test scheduling problem when using multiple BIST controllers. Note that our ILP formulation is very different from those of [5] [6] [8] [15] since we use logical constraints to define parallel and serial testing. Table I defines notations used in our discussion. The objective is to minimize total test time, i.e.,

minimize

$$\max_{\forall m_i} T_{E_i}$$

(1)

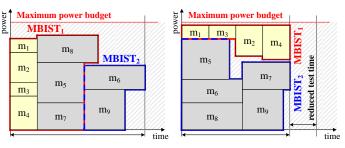

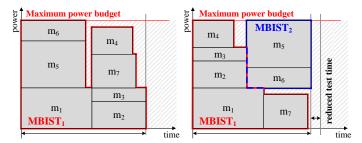

where  $T_{E_i} = T_{S_i} + T_{D_i}$ , and  $T_{S_i} \ge 0$ . We assume that a memory has test time proportional to its depth [17] and test power proportional to the square root of its size. Based on our studies, we see that allowing both serial and parallel testing of memories can reduce test time as illustrated in Figure 1.

<sup>1</sup>The mixture of serial and parallel testing induces what may be thought of as a *partial level-oriented strip packing problem*. (In the two-dimensional strip packing problem, (rectangular) items are packed into an "open-ended" rectangle of given height and infinite width, and the objective is to minimize width while packing all of the items into the rectangle [2].) To our knowledge, the DFT literature has not yet considered this partial level-oriented strip packing formulation.

<sup>2</sup>This being said, the test cost and the area/power overheads of memory BIST are rapidly drawing more attention to this topic.

$^{3}$ In [7], the estimation of test time without consideration of test scheduling leads to unnecessary expense of test time when there is power slack below the power constraint. Further, the placement of BIST logic at median x- and y-coordinates of all memory instances in [7] is oblivious to the underlying min-weight maximum-matching problem when path timing is considered.

TABLE I: Notations.

| Term            | Meaning                                                      |  |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------|--|--|--|--|--|--|--|

| М               | Set of memory instances                                      |  |  |  |  |  |  |  |

| $m_i$           | $i^{th}$ memory instance, where $1 \le i \le  M $            |  |  |  |  |  |  |  |

| xi              | Size of word in <i>m<sub>i</sub></i>                         |  |  |  |  |  |  |  |

| y <sub>i</sub>  | Number of words in <i>m<sub>i</sub></i>                      |  |  |  |  |  |  |  |

| В               | Set of memory BIST controllers                               |  |  |  |  |  |  |  |

| $b_k$           | $k^{th}$ memory BIST controller, where $1 \le k \le  B $     |  |  |  |  |  |  |  |

| $P^k$           | Set of partitions, (k-way partitioning)                      |  |  |  |  |  |  |  |

| $p_i$           | <i>i</i> <sup>th</sup> partition                             |  |  |  |  |  |  |  |

| $D(p_i)$        | Diameter of the $i^{th}$ partition $p_i$                     |  |  |  |  |  |  |  |

| $T_{S_i}$       | Test start time of $m_i$                                     |  |  |  |  |  |  |  |

| $T_{E_i}$       | Test end time of $m_i$                                       |  |  |  |  |  |  |  |

| $T_{D_i}$       | Test duration of <i>m<sub>i</sub></i>                        |  |  |  |  |  |  |  |

| $t_q$           | Instantaneous time                                           |  |  |  |  |  |  |  |

| $E(m_i)$        | Test power of $m_i$                                          |  |  |  |  |  |  |  |

| $E(t_q)$        | Total test power at time $t_q$                               |  |  |  |  |  |  |  |

| $E_{MAX}$       | Upper bound on total test power                              |  |  |  |  |  |  |  |

| $U_i(t_q)$      | Indicator whether $m_i$ is under testing at time $t_q$       |  |  |  |  |  |  |  |

| $V_i(t_q)$      | Indicator whether $t_q \ge T_{S_i}$                          |  |  |  |  |  |  |  |

| $W_i(t_q)$      | Indicator whether $t_q \leq T_{E_i}$                         |  |  |  |  |  |  |  |

| $B_{k,i}$       | Indicator whether $m_i$ is tested with BIST controller $b_k$ |  |  |  |  |  |  |  |

| $I_{k,i,j}$     | Indicator whether $m_i$ and $m_j$                            |  |  |  |  |  |  |  |

|                 | belong to the same BIST controller $b_k$                     |  |  |  |  |  |  |  |

| $L_{k,i,j}$     | Indicator whether $m_i$ and $m_j$ are tested in parallel     |  |  |  |  |  |  |  |

|                 | with the same BIST controller $b_k$                          |  |  |  |  |  |  |  |

| $F_{k,i,j}$     | Indicator whether $m_i$ is tested before starting test of    |  |  |  |  |  |  |  |

|                 | $m_j$ with the same BIST controller $b_k$                    |  |  |  |  |  |  |  |

| $Q_{k,i,j}$     | Indicator whether $T_{S_i} \leq T_{S_j}$                     |  |  |  |  |  |  |  |

| $N_L$           | Large integer                                                |  |  |  |  |  |  |  |

| N <sub>LL</sub> | Large integer $N_{LL} \gg N_L$                               |  |  |  |  |  |  |  |

| ε               | Positive and very small real number, $0 < \varepsilon \ll 1$ |  |  |  |  |  |  |  |

The ILP constraints are as follows.

**Maximum power constraint.** We use  $E_{MAX}$  to denote an upper bound on maximum available test power. The instantaneous testing power  $E(t_q)$  cannot exceed  $E_{MAX}$ , as indicated by constraint (2).  $E(t_q)$  is the sum of test power consumption for all memory instances  $m_i$  being tested at time  $t_q$ , as shown in Equation (3), where  $U_i(t_q)$  indicates whether  $m_i$  is being tested at time  $t_q$ , and  $E(m_i)$  is the test power of  $m_i$ . The constraint (4) ensures that all memories must be tested to obtain a valid solution.

$$E(t_q) \le E_{MAX}$$

$$E(t_q) = \sum_{m_i \in M} U_i(t_q) \cdot E(m_i)$$

(2)

where

$$U_i(t_q) = \begin{cases} 1, & T_{S_i} \le t_q < T_{E_i} \\ 0, & otherwise \end{cases}$$

(3)

$$\forall m_i, \ \sum_{\forall t_q} U_i(t_q) \ge 1$$

(4)

**BIST assignment constraint.** We use the constraint (5) to ensure that each memory is uniquely assigned to a BIST controller for testing.

Fig. 1: Example with nine memories and two BIST controllers showing test time reduction when both serial and parallel testing are allowed. The left figure shows test time when only parallel testing is allowed. The right figure shows the reduced test time by allowing both serial and parallel testing.

$B_{k,i}$  indicates whether  $m_i$  is assigned to BIST controller  $b_k$  for testing.

$$\sum_{\forall b_k} B_{k,i} = 1, \quad m_i \in M$$

where  $B_{k,i} = \begin{cases} 1, & \text{if } m_i \text{ assigned to } b_k \\ 0, & otherwise \end{cases}$  (5)

**Scheduling constraint.** We define three indicator variables  $I_{k,i,j}$ ,  $F_{k,i,j}$ , and  $L_{k,i,j}$  to constrain the order of testing between two memories  $m_i$  and  $m_j$  that are assigned to the same controller  $b_k$ . These ensure that  $m_i$  and  $m_j$  are tested either in series or in parallel.

$I_{k,i,j}$  indicates whether  $m_i$  and  $m_j$  share the same BIST controller  $b_k$ , and has a value of zero when this is true, as shown in Equation (6). If  $I_{k,i,j} = 0$  (i.e.,  $m_i$  and  $m_j$  share the same BIST controller),

- *F<sub>k,i,j</sub>* indicates whether *m<sub>i</sub>* is tested before *m<sub>j</sub>* when tested serially; or

- $L_{k,i,j}$  indicates whether  $m_i$  and  $m_j$  are tested in parallel,

as shown in Equations (6)–(8). When  $I_{k,i,j} = 1$ , there is no scheduling relationship between  $m_i$  and  $m_j$ .

$$\mathbf{I}_{k,i,j} = \begin{cases} 0, & (B_{k,i} = 1) \land (B_{k,j} = 1) \\ 1, & otherwise \end{cases}$$

(6)

$$\mathbf{F}_{k,i,j} = \begin{cases} 1, & (B_{k,i} = B_{k,j} = 1) \land (T_{E_i} \le T_{S_j}) \\ 0, & otherwise \end{cases}$$

(7)

$$(L_{k,i,j} + F_{k,i,j} + F_{k,j,i}) \cdot (1 - I_{k,i,j}) = 1$$

, where  $i \neq j$  (8)

# IV. CO-OPTIMIZATION OF TEST SCHEDULING AND MEMORY BIST LOGIC PLACEMENT

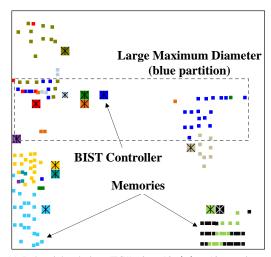

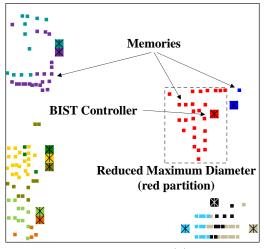

We now describe our heuristic methodology for the co-optimization of test scheduling and memory BIST logic placement. Modern semiconductor chips contain hundreds of embedded memories scattered across the entire die. These memories can have various widths and depths, and can belong to different clock and logic hierarchies. Both the number and complexity of memory instances make the test scheduling problem extremely hard. We utilize a "divideand-conquer" approach to develop a three-step heuristic method that (1) initially partitions all memories based on physical information using MLPart [4] [24]; (2) solves the test scheduling problem using an ILP formulation, followed by additional partitioning for better test time optimization; and (3) places memory BIST logic for each partition to minimize wirelength between memory BIST logic and memories. The goals of our heuristic approach are (1) minimization of test time, (2) reduction of number of partitions (i.e., number of BIST controllers), and (3) minimization of wirelength between each BIST and memories. We have developed a solver that uses command-line options as shown in Table II. Algorithms 1-3 outline our heuristic modeling approach.

TABLE II: MBIST solver command-line options.

|          | 1                                                     |

|----------|-------------------------------------------------------|

| -numMaxP | Maximum possible number of partitions for the design  |

| -numMinP | Minimum required number of partitions for the design  |

| -maxMemP | Upper bound of number of memories in a partition      |

| -minMemP | Lower bound of number of memories in a partition      |

| -maxD    | Maximum allowed diameter for a partition ( $\mu$ m)   |

| -conP    | Power constraint                                      |

| -gridS   | Size of grid cell ( $\mu$ m) for BIST logic placement |

| -t       | Tolerance (%) for balanced partitioning               |

| -longD   | Longer diameter criterion for edge weight $K_4$       |

| -shortD  | Shorter diameter criterion for edge weight $K_6$      |

#### A. Memory Partitioning

Memory partitioning is the "divide" step in our heuristic approach. We divide memory instances into k partitions using *MLPart* [4] [24], a min-cut hypergraph partitioner based on the multilevel Fiduccia-Mattheyses hypergraph partitioning [24] algorithm. The input to *MLPart* is a hypergraph *G*, where each node in *G* corresponds to a memory in the design (Algorithm 2). We define edge weights based on parameters such as memory shape, depth, power, location, etc. We expect that partitioning memories that have the same shape or depth

#### Algorithm 1 Memory Partitioning

```

Procedure Partitioning(M)

Input: M, numMaxP, numMinP, maxMemP, maxD, K_{\{1-6\}}

Output: Pout

1: for n = numMaxP to numMinP do

P^1 \leftarrow \text{single partition of } M;

2:

for k = 1 to n - 1 do

3:

G \leftarrow null; p_j \leftarrow \emptyset;

4.

if \max_{p_i \in P^k} \{ |p_i| \} > maxMemP then

5:

p_j \leftarrow \arg\max_{p_i \in P^k} \{|p_i|\};

else if \max_{p_i \in P^k} \{D(p_i)\} > \max D then

6:

7:

p_j \leftarrow \operatorname{arg\,max}_{p_i \in P^k} \{ D(p_i) \};

8:

9.

else

10:

p_{j_1} \leftarrow \operatorname{arg\,max}_{p_i \in P^k} \{ |p_i| \}; \ p_{j_2} \leftarrow \operatorname{arg\,max}_{p_i \in P^k} \{ D(p_i) \};

p_j \leftarrow \arg\min_{p_{j_1}, p_{j_2}}(p_{j_1}, \operatorname{cut}, p_{j_2}, \operatorname{cut});

end if // partition p_j is the input for the next bipartitioning

11:

12:

P^{k+1} \leftarrow P^k \setminus \{p_i\};

13:

14:

for criterion index r = 1 to 6 do

15:

G \leftarrow GenerateHypergraph(p_i, r, G);

16:

end for

\{p_j, p_k\} \leftarrow MLPart(G);

P^{k+1} \leftarrow P^{k+1} \cup \{p_j\} \cup \{p_k\};

17:

18:

end for

19:

D_{max} \leftarrow \max_{p_j \in P^n} \{D(p_j)\}; \ // P^{k+1} = P^n

20:

if D_{max} > maxD then

21:

if n == numMaxP then

22:

return PnumMaxP

23:

24:

else

25:

return P^{n+1};

26:

end if

27:

end if

28: end for

29: return P<sup>numMinP</sup>:

```

# **Algorithm 2** Construct Weighted Hypergraph (for $r^{th}$ criterion)

**Procedure** GenerateHypergraph $(p, r, G_{in})$

Input: p, criterion index r, (hyper)edge weight  $K_r$ , hypergraph  $G_{in}$ Output: G

```

1: G \leftarrow G_{in};

```

- 2: for all  $m_i \in p$ , i = 0 to |p| 1 do

- 3:  $v_i \leftarrow mapping(m_i); // \text{ node } v_i \text{ corresponds to } m_i \text{ in partition } p$ 4: add node  $v_i$  to G;

- 5: *visited*( $v_i$ )  $\leftarrow$  false;

- 6: end for

13: 14:

- 7: **for** i = 0 to |p| 1 **do**

- 8:  $V_{conn} \leftarrow 0; e \leftarrow null;$

- 9:  $V_{conn} \leftarrow \{v_i\}; // v_i \text{ is reference node}$

- 10:  $visited(v_i) \leftarrow true;$ 11: **for** j = 0 to |p| - 1 **do**

- 12: **if**  $i \neq j$  **then**

- if  $(visited(v_i) == false) || (r \ge 4)$  then

- if  $v_i$  and  $v_j$  satisfy criterion crit<sub>r</sub> then

- 15:  $V_{conn} \leftarrow V_{conn} \cup \{v_j\};$   $|| V_{conn}$  is set of nodes that satisfy  $crit_r$  w.r.t.  $v_i$ 16:  $visited(v_j) \leftarrow true;$ 17: end if 18: end if 19: end if 20: end for 21: if  $|V_{conn}| \ge 2$  then

- 22:  $e \leftarrow \text{connect all } v \in V_{conn} \text{ as (hyper)edge;}$ 23:  $weight(e) \leftarrow K_r;$

- 24: add (hyper)edge e to G;

```

25: end if

```

```

26: end for

27: return G;

```

27: return G

into one group leads to higher opportunity to minimize test time. This is because memories with the same depth can be tested in parallel and memories with the same power can be tested in serial, which minimizes idle space in test time and power. In addition, we assign larger weights to edges when memories are closer.

#### Algorithm 3 Test Scheduling

| <b>Procedure</b> Scheduling $(M, P^k)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input: M, P <sup>k</sup> , numMaxP, GroupSizes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Output: P <sup>out</sup> , test scheduling for each partition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1: $numAddBIST \leftarrow numMaxP -  P^k ;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2: while $numAddBIST > 0$ do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3: for all $p_i \in P^k$ do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4: for all $s_i \in GroupSizes$ do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5: $GroupMemories(s_i)$ ; // grouping memories with size $s_i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6: $Sol_{p_i,s_i} \leftarrow SolveMBISTILP(1);$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7: $\{Sol_{p_{i_1},s_j}, Sol_{p_{i_2},s_j}\} \leftarrow SolveMBISTILP(2);$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8: end for $(1,1,1,2,1,1,2,1,1,2,1,1,2,1,1,2,1,1,2,1,1,2,1,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,1,2,$ |

| 9: $Sol_{p_i} \leftarrow Sol_{p_i,s_1,best};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10: $Sol_{p_{i_1}} \leftarrow Sol_{p_{i_1},s_2,best}; Sol_{p_{i_2}} \leftarrow Sol_{p_{i_2},s_2,best};$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11: $Gain_{p_i} \leftarrow Sol_{p_i}.cost - \max(Sol_{p_i}.cost, Sol_{p_i}.cost);$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12: end for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13: choose $p_i \in P^k$ that has the largest $Gain_{p_i}$ ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14: <b>if</b> the largest $Gain_{p_i} == 0$ <b>then</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15: break;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16: <b>end if</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17: $\{p_a, p_b\} \leftarrow$ result of partition $p_i \in P^k$ that has the largest $Gain_{p_i}$ ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18: $P^k \leftarrow (P^k \setminus p_i) \cup p_a \cup p_b;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19: $numAddBIST \leftarrow numAddBIST - 1;$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 20: end while                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21: $P^{out} \leftarrow P^k$ ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table III summarizes the edge weights used in *G*, each corresponding to one criterion.  $crit_1$ ,  $crit_2$ , and  $crit_3$  are the criteria of hyperedges between memories that have the same shape  $(crit_1)$ , depth  $(crit_2)$  and test power  $(crit_3)$ , respectively. In addition,  $crit_4$ ,  $crit_5$ , and  $crit_6$  specify the criteria of edges between pairs of memories with distances  $\leq longD$   $(crit_4)$ ,  $\leq (longD + shortD)/2$   $(crit_5)$ , and  $\leq shortD$  ( $crit_6$ ), respectively. In our implementations, we set longD and shortD to  $1000\mu m$  and  $250\mu m^4$ , respectively. The weights of hyperedges (respectively, edges) are additive, e.g., memories that have the same shape are connected by hyperedges with weight  $K_1 + K_2 + K_3$  since memories having the same shape also have the same depth and power.<sup>5</sup>